Rostec Engineering Administration: Christianehøj 43, 2860 Søborg, Denmark - Email rostec@rostec.dk - Phone +45 3967 6438

Features

* 3 inputs into 24 outputs (3 groups of 8).

* Distributes word clocks from 1 Hz to 25 MHz.

* Converts sine waves to square waves.

* Distributes AES3id with sample rates ranging from 8 kHz to 768 kHz.

* Extracts word clock from SPDIF/AES3id/AES3 at sample rates from 32 kHz to 192 kHz.

* Balanced inputs for ground noise cancellation.

* The Inputs have "sweet spot" detectors, providing auto-slicing and signal clean-up.

* Inputs accept from 0.2 Volts to 10 Volts.

* Individual selectable output level for each output group. Choose between TTL for word clocks or bipolar for AES3id.

* Ultra high speed long haul output buffers.

* 75 ohms output via BNC connectors.

* Latency from input to output is 30 nsec

* Separate power supplies for inputs and for each output group.

* Linear low noise power supplies.

* Short circuit proof. Self protecting. Individual thermal protecting for each output group.

* Inputs and outputs are ESD protected to 23 kV, IEC 61000-4-2 and 15 A surge, IEC 61000-4-5

* 19" sturdy steel metal casing

* Affordable price

CAD324 Clock and AES3id Distribution Amplifier.

The CAD324 is a high quality distribution amplifier designed to operate in a broadcast, video or audio studio installation. It

distributes clocks and AES3id with the correct output levels and output formats. It has 3 inputs and 24 outputs configured as 3

groups of 8 outputs. Any of the 3 output groups can be freely selected to connect to any of the 3 inputs.

The inputs accept digital clocks from 0.2 Volts to 10 Volts and digital audio at SPDIF, AES3id and AES3 (11) levels. It distributes

clocks, from 1Hz (*) to 25 MHz. This means that all standard audio clocks, Telecom clocks and GPS clocks are within its operating

range. It also distributes AES3id with sample rates ranging from 8 kHz to 768 kHz.

The inputs can be selected as balanced or unbalanced by a switch on the back

panel. Each input features a true balanced high-speed comparator with

hysteresis and a "sweet spot" detector, which performs an accurate auto-slicing

of the input.

This means that the input circuit automatically chooses the most useful part of

the input signal as the reference point, thus being able to clean-up and

reconstruct a ringing and noisy input signal into a perfect output signal.

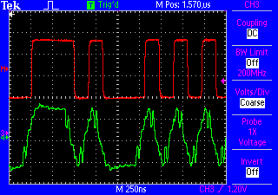

The lower trace is a 48 kHz AES input, badly distorted and noisy.

The upper trace is the clean reconstructed signal at the output.

But apart from being a genuinely high quality distribution amplifier, the CAD324 has some other really nifty features:

* It extracts a low jitter word clock from an incoming SPDIF, AES3id or AES3 (11), as long as the sample rate is within the range

of 32 kHz to 192 kHz. The word clock extraction is performed by hardware logic directly on the AES signal. This method

introduces the least possible jitter in the extraction process - in the order of a few picoseconds.

* It converts a sine wave input into a TTL square wave with excellent jitter specification. Very useful in connection with GPS

receivers.

* It converts a balanced AES3 input signal into an AES3id output signal.

* It also converts a SPDIF signal into an AES3id signal, but a couple of issues must be considered. The CAD324 converts the

SPDIF electrical level into the correct AES3id electrical level, but SPDIF and AES3id exhibit differences in their channel status

bits like consumer /professional status and copy protection etc. Note that the CAD324 does NOT convert these status bits! It does

NOT change any data embedded in the signal whatsoever!

However, in most cases it will be no problem. The audio data encoding and block structure of SPDIF and AES3id are identical,

and the differences in channel status bits are normally ignored by professional equipment.

The input circuit and each of the 3 output groups have their own individual power supply. The separate power supplies and

separate internal ground planes create an efficient isolation barrier between groups, eliminating crosstalk and jitter transfer when

different sampling frequencies and different data structures are distributed through the same unit.

The 24 individual output buffers are ultra high speed with accurate output impedances, making them well suited for long haul. The

output levels of each individual group can be selected by push buttons on the front: 75 ohms TTL compatible for word clocks, and

75 ohms bipolar for AES3id.

The input and output circuits are state of the art, resulting in a 40 MHz overall bandwidth. The latency from input to output is

approx. 30 nsec. The rise time of the output pulse is less than 3 nsec into 75 ohms with an overshoot/undershoot of less than 5%.

The fast rise time makes the output signal appear well defined and clear cut seen from a receiver's point of view. This enables the

receiver to react to the signal with maximum accuracy and minimal jitter.

(*) At 1 Hz the input sensitivity is TTL level.